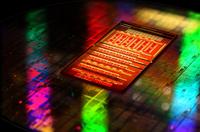

千兆集成电路IC平行SPICE模拟工具究竟拥有何等内涵

有关NanoSpice此一适用於千兆规模集成电路IC设计的平行SPICE模拟工具,究竟拥有何等内涵,则由ProPlus董事长刘志宏进行深入介绍。

刘志宏指出,每隔一年,晶片内的晶体管数量持续骤增,而每个晶粒(Die)上的Cache数量也逐步提高,这也意谓设计人员必须随之提高模拟验证的性能、容量与精确度,同时亦需加快电路设计的速度;表面看来,这些任务理应如此,似无特殊之处,但当中其实潜藏莫大挑战,比方说,电路速度的提升,代表信号变化率一併走高,模拟验证时间理应更短,但碍於设计週期比起从前拖得更长,使得鱼与熊掌难以兼顾。

「时至今日,诸如低电压(Low Voltage)、低耗电(Low Power)等新一代设计需求,使得製程变异幅度加剧,导致执行电路模拟,不能再像从前仅求『差不多』即可,否则就容易形成Miss Target。」刘志宏说。

在此前提下,设计人员若未顾及这些细微变化,恐造成无穷后患;此外,过往设计人员看待电晶体,不过就是一道大开关,如今每个Terminal都有电流,也让模拟过程所需处理的元件更显复杂,必须善加提高各个Terminal验证之精度,驱使身為EDA方案供应商的ProPlus,自知需要设法提出更完善的工具,协助用户克服诸多严峻挑战,使得NanoSpice因而应运而生。