三维集成电路IC(3D-IC)上篇

一种三维集成电路IC(3D-IC)是两层或更多层的有源电子元件的芯片中,同时在垂直和水平方向上都集成到一个单一的电路。 半导体行业的激烈追求在许多不同的形式,由于这种新兴技术的完整定义还是有点流体。

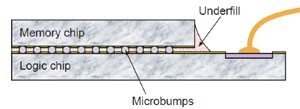

倒装芯片,内存逻辑

谈的是第一种方法翻转一个芯片,将其附加到另一个的顶部。 这是通过创建,每个芯片上的连接部位,生长(通常是铜)微凸创建死死互连间距约50um的。 这项技术是在数码相机芯片的大用户。 CCD图像传感器的实际减薄到如此地步,它是透明的光,然后被连接到图像处理芯片。 从相机透镜的光穿过硅互连等,这是所有的传感器的另一侧通畅的CCD。

这种方法也被用于把一个翻转内存芯片到逻辑芯片(见图片)。 这不是众所周知的,但苹果A4芯片内置这样,顶部处理器/逻辑芯片上的内存。 现在有标准化委员会的工作格局微凸,使用的DRAM(KToolbar中的DRAM标准引脚方式),使来自不同制造商的DRAM应该互换。 不像图片中,颠簸都朝向中心的模具,这样的模式是不受实际的裸片尺寸之间可能会有所不同制造商之间不同世代的设计。

尽管这一技术是正式三维的,因为有两个芯片,它不要求任何连接通过任何芯片,是一种退化的情况。

通过硅通孔(TSV)

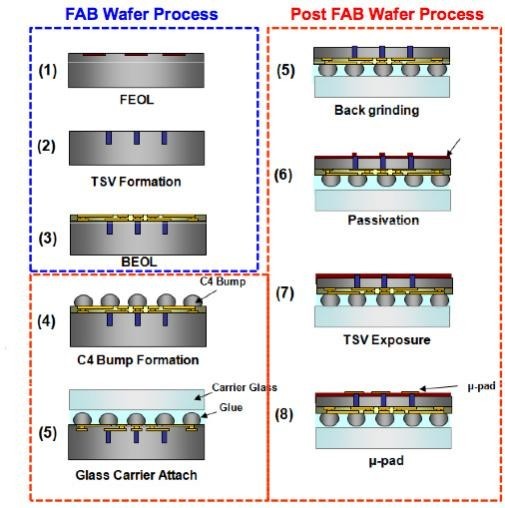

真正的3D芯片的关键技术是通过硅通孔(TSV)。 这是一个通过从晶片的前侧(通常是连接到下金属层)通过在晶片和从后面。 TSV的直径为1?10um的不同,从5到10倍的宽度与深度。 到晶片上形成的孔,内衬有绝缘体,,然后填充有铜或钨。 最后薄化晶圆到TSV的背面暴露。 请注意,这意味着晶片本身结束了仅10-100um的厚。 硅是脆性的,所以面临的挑战之一是这本薄薄的晶圆处理晶圆厂中,当他们被运到组装房子。 变薄和之前,在某些情况下,可能会被再次分离在组装过程中,必须在晶片键合到一些更强大的基板(玻璃或硅)。 薄化晶圆,使用CMP(化学机械抛光,如何进行平坦化,在一个正常的半导体工艺中金属层之间的相似),直到TSV的几乎暴露。 然后,更多的硅被蚀刻掉,以显示TSV的自己。

上述图片(点击为更大的图像)显示了三星的做法。 前段制程(这意味着前端线,这意味着晶体管是做前端设计无关)前完成。 所以晶体管都创建。 然后,TSV的形成。 后段制程(这意味着后端互连线,意味着是做后端设计无关)。 互连完成后,然后微凸被创建。 将晶片粘到玻璃载体。 的背面,然后研磨,钝化层被应用,这被蚀刻以暴露TSV的,然后创建micropads的。 TSV的晶体管和互连之间形成,这方法被称为TSVmiddle的。 还有TSVfirst(建设之前晶体管)和TSVlast(他们持续操练他们通过所有的互连以及基板)。

TSV的设计问题有两个。 首先是他们的排除周围地区。 通过登场通过的有效面积,通常是通过一些金属层。 由于制造商的详细信息,一个相当大的区域,必须留下TSV周围,这样它不损坏已经沉积层的情况下,可以制造。 第二个问题是,在制造过程中强调的方式,可以改变晶体管的阈值附近的任何地方,从而改变了该芯片的性能在一定的不可预知的方式在硅衬底。